捷配PCB分享提升PCB可测试性实用设计策略

为什么可测试性对PCB设计很重要?

PCB的设计不仅要关注功能实现、电气性能和可制造性,还必须考虑可测试性。可测试性指的是电路板在制造后能否快速、准确、低成本地进行功能验证、故障定位和质量检验。对很多产品来说,测试环节决定了交付效率和返修成本。

如果没有良好的可测试性,即使电路设计本身没有问题,也可能在量产中出现大量误判、漏测或返工,带来时间和金钱的浪费。特别是在自动化测试和批量测试中,可测试性设计是保障产线效率和质量的关键。

因此,从最初的原理图设计阶段开始,就应将可测试性作为一项核心考虑。

二、PCB测试的基本原理和类型

1. 电路板测试方式分类

PCB常见的测试方式主要有以下几种:

- ICT(In-Circuit Test,在线测试):通过探针接触测试点,检测元件开路、短路、电阻、电容、电感等参数;

- FCT(Functional Test,功能测试):模拟实际运行环境,检测整个电路的功能是否符合设计;

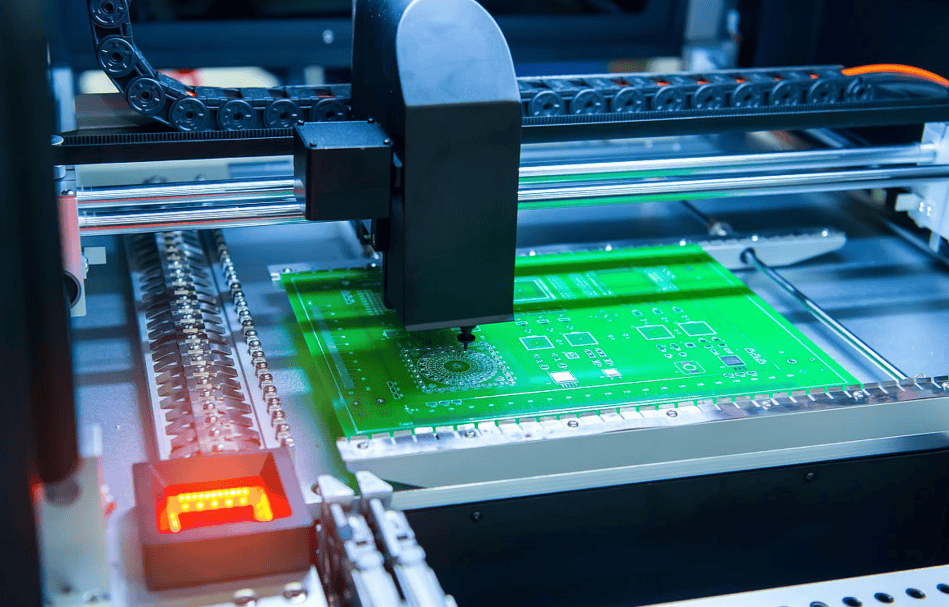

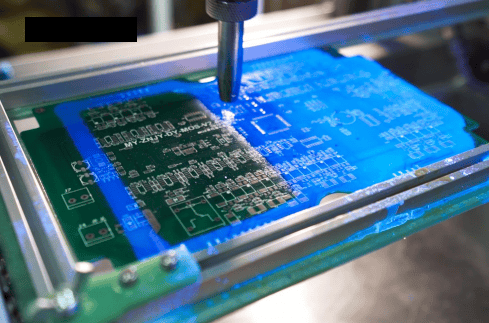

- Flying Probe Test(飞针测试):适合小批量或原型板,不需针床,灵活性高;

- Boundary Scan(边界扫描):通过芯片的JTAG接口进行逻辑级测试;

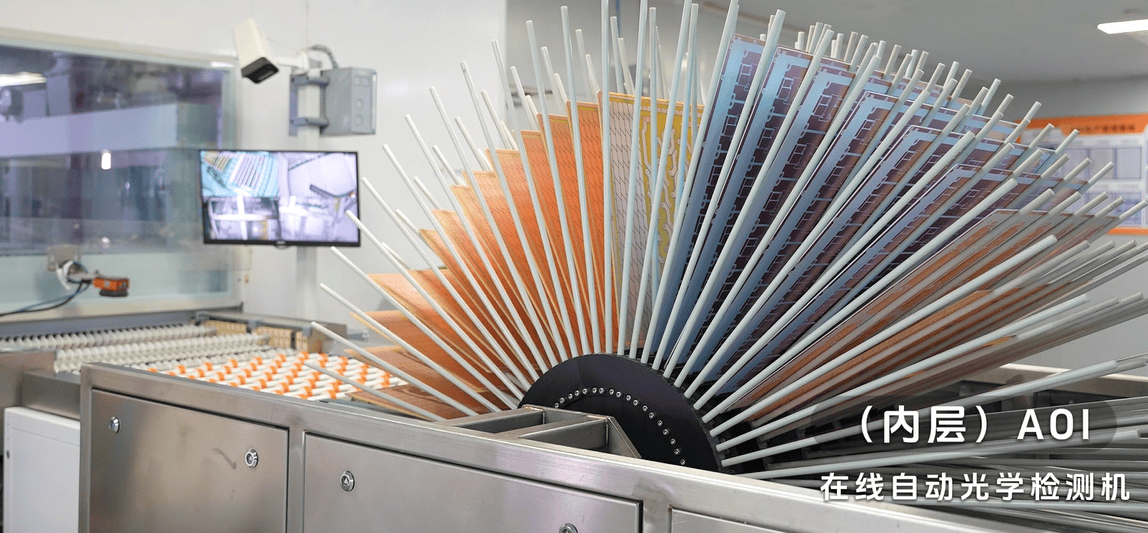

- AOI(自动光学检查):通过相机检查焊接缺陷、器件错位、极性错误等;

- X-Ray测试:检测BGA焊点、夹层空洞等不可见缺陷。

每种测试方法都有不同的适用范围,设计中要根据产品特性和测试资源选择合适方式。

2. 可测试性设计的核心要点

提高PCB的可测试性,本质上就是在设计时提前考虑以下问题:

- 是否能为每个关键节点提供稳定的探测点;

- 是否保证了测试信号的隔离性与一致性;

- 是否为探针、夹具等物理结构预留了足够空间;

- 是否考虑了测试程序对电路状态的控制路径;

- 是否有易于自动化分析的信号结构。

这些设计细节决定了后续测试能否顺利开展。

三、提升可测试性的设计方法

1. 设置充分的测试点

测试点是测试系统连接电路的关键。设计中应在每个重要信号、电源轨、地线、控制信号、时钟线上设置测试点。

建议:

- 每个信号至少设置一个单独的探测点;

- 使用焊盘直径1.0 mm左右,便于针床或飞针探测;

- 测试点可用专用焊盘,也可在元件引脚上加标记;

- 对于密集区域,可使用Via-in-pad或微型测试点。

在布线密度较高时,测试点位置需要提前规划,避免后期无处可加。

2. 避免测试点遮挡或失效

如果测试点被元器件、贴片封装遮挡,将导致无法测试。所以需要:

- 将测试点放在器件外侧或空白区域;

- 与元件之间保持足够距离,一般不少于1.5 mm;

- 禁止将测试点布在BGA下方;

- 对于关键器件,可设计测试延长引出线。

此外,所有测试点表面应无阻焊覆盖,以保证探针接触可靠。

3. 保证测试点的电连接清晰

测试点必须连接在目标网络上,不能仅连接元件引脚或中间节点。为保证测试精度,建议:

- 避免多个测试点连接到同一网络;

- 为测试用的上拉、下拉电阻单独设置测试点;

- 电源和地的测试点要分布均匀,便于参考电位;

- 有屏蔽或保护电路的信号,应在前级设置测试点。

同时,不应出现悬空测试点,即与实际电路无连通的假焊盘。

4. 统一测试点布局,便于夹具制作

在量产测试中,常用针床夹具。为了简化夹具设计,提高对准精度,应使测试点分布整齐,排列规则。

设计建议:

- 测试点尽量排列成矩阵、行列;

- 区分模拟、数字、电源信号的区域;

- 将功能测试和ICT测试的点分开排布;

- 所有测试点应尽可能集中在同一面;

- 重要测试点使用定位孔或参考点对齐。

统一的布局不仅利于夹具定位,也有助于程序维护。

5. 设计测试控制信号

在FCT测试中,需要控制电路的运行状态。可以设置如下控制点:

- 强制复位引脚;

- 电源开关控制点;

- 模拟量输入点;

- 通信接口(如UART、I2C、SPI)测试引脚;

- 测试固件触发脚。

这些信号可通过跳线、拨码开关或测试点实现。设计中应明确测试路径与工作路径分离,避免测试状态干扰正常运行。

6. 为测试预留接口

复杂产品中,可以预留标准通信接口,便于调试和功能测试。常见接口包括:

- JTAG;

- UART串口;

- USB调试接口;

- SWD(ARM Cortex系列);

- 特定的模拟接口。

这些接口既可用于测试,也可用于固件下载、调试分析。接口应结构稳固、易插拔、占位小。

7. 加入可测试性分析环节

使用EDA工具的DFT(Design for Testability)分析功能,可以在设计阶段评估测试覆盖率。

可以通过:

- 自动检查未设置测试点的网络;

- 分析相邻信号间串扰风险;

- 检查通孔阻焊影响;

- 模拟夹具探针接触区域;

- 生成测试点网表与BOM数据。

分析完成后再修改设计,有助于减少测试遗漏和后期返工。

四、可测试性设计中的常见错误与优化建议

错误1:没有测试点或过少

一些设计仅在电源和复位点加测试点,忽略了功能信号测试,后期无法有效判断问题。建议所有关键网络都加最少一个探针。

错误2:测试点被焊盘或元件遮住

如果测试点被贴片器件、热缩管、电容挡住,就算布了也无法探测。应确保测试点位置暴露,表面无遮挡。

错误3:测试点重叠或太密

测试点之间距离太近,会导致夹具探针干涉、短路。建议测试点中心距大于2 mm,必要时适当简化非关键信号点。

错误4:测试点位置不一致

如果相同产品的多个版本测试点位置变化,会造成夹具不兼容,增加测试成本。测试点布置应保持稳定性。

良好的可测试性不仅提升产线效率,也增强后期维修能力,是PCB产品设计不可或缺的一部分。在捷配PCB,我们随时为您的项目提供量身定制的高质量 PCB 制造和组装服务,为您的旅程提供支持。