韩国研究团队成功开发出无电容Micro LED显示架构

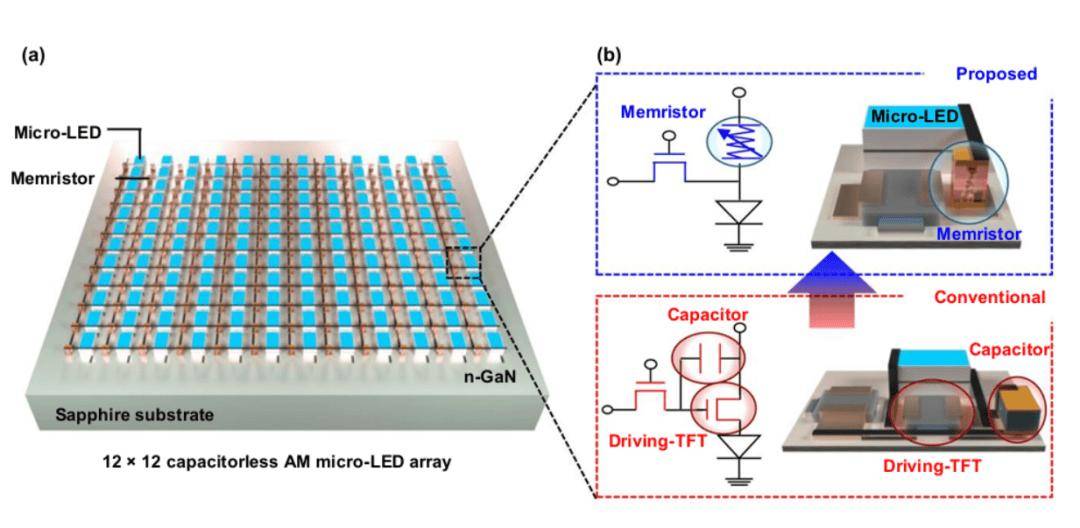

CINNO Research产业资讯,在显示技术向“超高清、低功耗、微型化” 迈进的关键阶段,一项来自韩国科研团队的突破性成果引发行业高度关注。近日,高丽大学、三星显示与印度希瓦吉大学等机构联合在《极端制造》期刊上发表研究论文,提出一种基于碲化锗(GeTe)忆阻器的无电容AMMicro-LED显示架构。该技术通过单片集成亚伏级忆阻器驱动像素,不仅成功替代传统晶体管- 电容组合,更实现了48.1%的功耗降低、93.1%的超高开口率,以及6000PPI以上的像素密度潜力,为AR/VR、智能穿戴、医疗影像等高端显示场景提供了全新解决方案。

Micro-LED显示困局:传统架构难破 “三难” 瓶颈

作为被业界公认的“下一代显示技术标杆”,Micro-LED凭借其优异的光电性能 —— 包括 1000nits 以上的峰值亮度、纳秒级响应速度、百万级对比度及超过10万小时的使用寿命 —— 自诞生以来便承载着突破现有显示技术局限的期待。目前,Micro-LED已在超大尺寸电视、拼接屏等领域实现初步应用,但在AR/VR头显、智能手表、医疗微创手术显示器等对 “分辨率、功耗、体积” 要求严苛的场景中,却长期受限于三大核心瓶颈,商业化进程缓慢。

瓶颈一:像素密度受限于“晶体管 + 电容” 架构,传统AMMicro-LED显示采用 “2T-1C”(2个晶体管 + 1个电容)的单元像素设计,其中电容负责存储电荷以维持像素亮度,晶体管则负责信号开关与电流调控。然而,随着像素尺寸缩小至10μm以下,电容的存储容量与晶体管的短沟道效应问题愈发突出 —— 电容面积若按比例缩小,会导致电荷泄漏加剧,需频繁刷新;晶体管尺寸减小则会引发电流波动,影响显示稳定性。这种 “元件尺寸与性能” 的矛盾,使得传统架构下Micro-LED像素密度难以突破3000PPI,远不能满足AR/VR设备对 5000PPI以上分辨率的需求。

瓶颈二:高功耗源于电容的固有缺陷,电容的电荷泄漏特性是传统Micro-LED显示功耗居高不下的核心原因。为维持像素亮度稳定,驱动电路需每帧(约16.7ms)对电容进行一次电荷补充,即 “刷新操作”。数据显示,一台采用传统架构的5.5英寸2K分辨率Micro-LED显示屏,仅刷新操作消耗的功耗就占总功耗的35%以上。在AR/VR头显等依赖电池供电的设备中,高功耗直接导致续航时间缩短至2-3小时,成为用户体验的关键短板。

瓶颈三:制造复杂度推高成本与良品率风险,传统Micro-LED 显示的制造流程涉及两大关键难题:一是 “芯片转移”,需将数百万颗微米级LED芯片从蓝宝石衬底转移至驱动背板,现有 “拾取 - 放置” 技术存在效率低、机械对准误差大的问题,转移良率难以突破99.99%;二是 “多层集成”,晶体管与电容需通过多次光刻、退火、薄膜沉积等工艺制备,仅2T-1C架构就需 13 道掩膜工序,不仅增加制造成本,还易因工艺步骤过多导致缺陷率上升。据行业测算,传统Micro-LED显示屏的制造成本是同尺寸OLED的3-5倍,严重制约其大规模普及。

尽管行业曾尝试通过“单片集成晶体管”、“CMOS 驱动背板” 等方案突破瓶颈,但前者面临晶体管与LED芯片的热匹配问题(LED工作时局部温度升高会导致晶体管性能漂移),后者则因硅衬底与GaN外延层的热膨胀系数差异,导致芯片剥离与封装难度陡增,均未能实现根本性突破。

技术突破1:GeTe忆阻器实现 “单元件双功能替代”

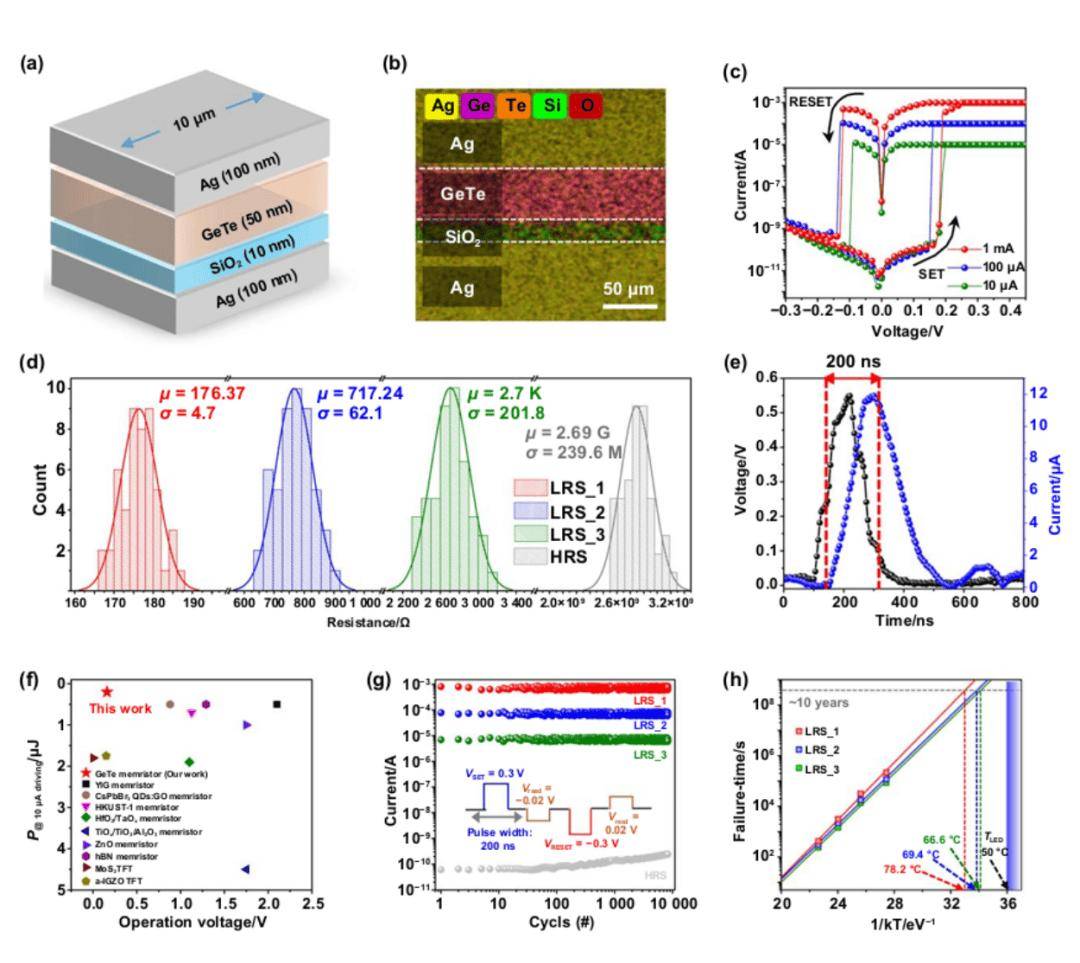

面对传统架构的固有缺陷,上述韩国联合研究团队创新性地提出“以忆阻器替代晶体管 + 电容” 的核心思路,选择GeTe(碲化锗)作为忆阻器核心材料,凭借其独特的 “电阻态可控性” 与 “电荷保持能力”,成功实现了单元件对传统架构中两个核心元件的功能替代,从根本上重构了MicroLED的驱动逻辑。

核心突破1:亚伏级运行,功耗降低48.1%

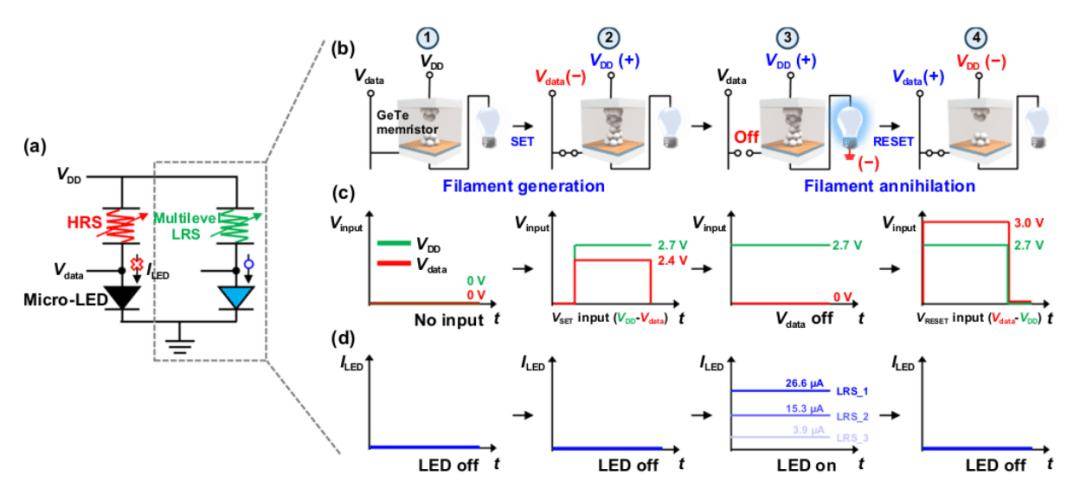

更关键的是,GeTe忆阻器无需依赖电容存储电荷 —— 其内部形成的 “导电细丝” 在SET操作后可半永久稳定存在,直至施加RESET电压才会湮灭。这意味着像素亮度可在无任何刷新操作的情况下维持,彻底消除了传统架构中因刷新产生的额外功耗。测试数据显示,在12×12 Micro-LED阵列测试中,GeTe忆阻器驱动方案的每帧功耗为21.9mW,较传统IGZO TFT方案的42.1mW降低48.1%;在 “常亮显示”(如智能手表的时间界面)场景中,功耗优势更可扩大至408%,续航时间有望延长3-4倍。

核心突破2:多电阻态特性,实现亮度精准调控

为满足显示场景对“灰度级” 的需求,研究团队通过调控GeTe忆阻器的限流电流,成功实现了 “1个高阻态 + 3个低阻态” 的四档电阻调节,对应Micro-LED的 “熄灭” 与 “低、中、高” 三档亮度。测试结果显示,在2.7V的工作电压下,忆阻器处于高阻态(HRS)时,Micro-LED的驱动电流仅为21nA,几乎无发光;处于低阻态 LRS_1(176.3Ω)时,电流可达26.6μA,发光强度达到380nits;LRS_2(717.2Ω)与LRS_3(2.7kΩ)则分别对应15.3μA、3.93μA的电流与270nits、160nits的亮度,亮度分级清晰且稳定。

这种多电阻态特性不仅简化了灰度调节电路,还具备进一步扩展的潜力。研究团队指出,通过优化限流电流的调节精度(如采用增量步长脉冲编程技术),GeTe忆阻器可实现256级以上的电阻态控制,完全满足全彩色显示对灰度级的需求。

核心突破3:高稳定性与工艺兼容性,扫清量产障碍

商业化显示器件对“长期稳定性” 的要求极为严苛,而 GeTe 忆阻器在这一维度的表现同样突出。论文数据显示,该器件在 25℃环境下,各电阻态的电流稳定性可维持105秒(约27.8小时),通过阿伦尼乌斯热稳定性模型推算,在Micro-LED典型工作温度(50℃)下,数据保持时间可超过10年;同时,其开关循环耐力达到104次,虽暂未达到商用显示10⁹次的要求,但研究团队表示,通过优化GeTe薄膜的结晶度与电极界面设计,耐力有望提升至10¹² 次,满足50000小时以上的使用需求。

在制造工艺兼容性上,GeTe忆阻器更是展现出显著优势。与传统TFT需要300℃以上高温退火不同,GeTe忆阻器的制备可在室温下完成,且无需复杂的离子注入或掺杂工艺。研究团队采用 “台面刻蚀- 钝化层沉积 - 忆阻器集成” 的单片工艺,仅需9道掩膜工序即可完成12×12 Micro-LED阵列的制备,较传统2T-1C架构减少4道关键工序,不仅降低了工艺复杂度,还避免了芯片转移过程中的机械损伤风险,良率提升至95%以上。

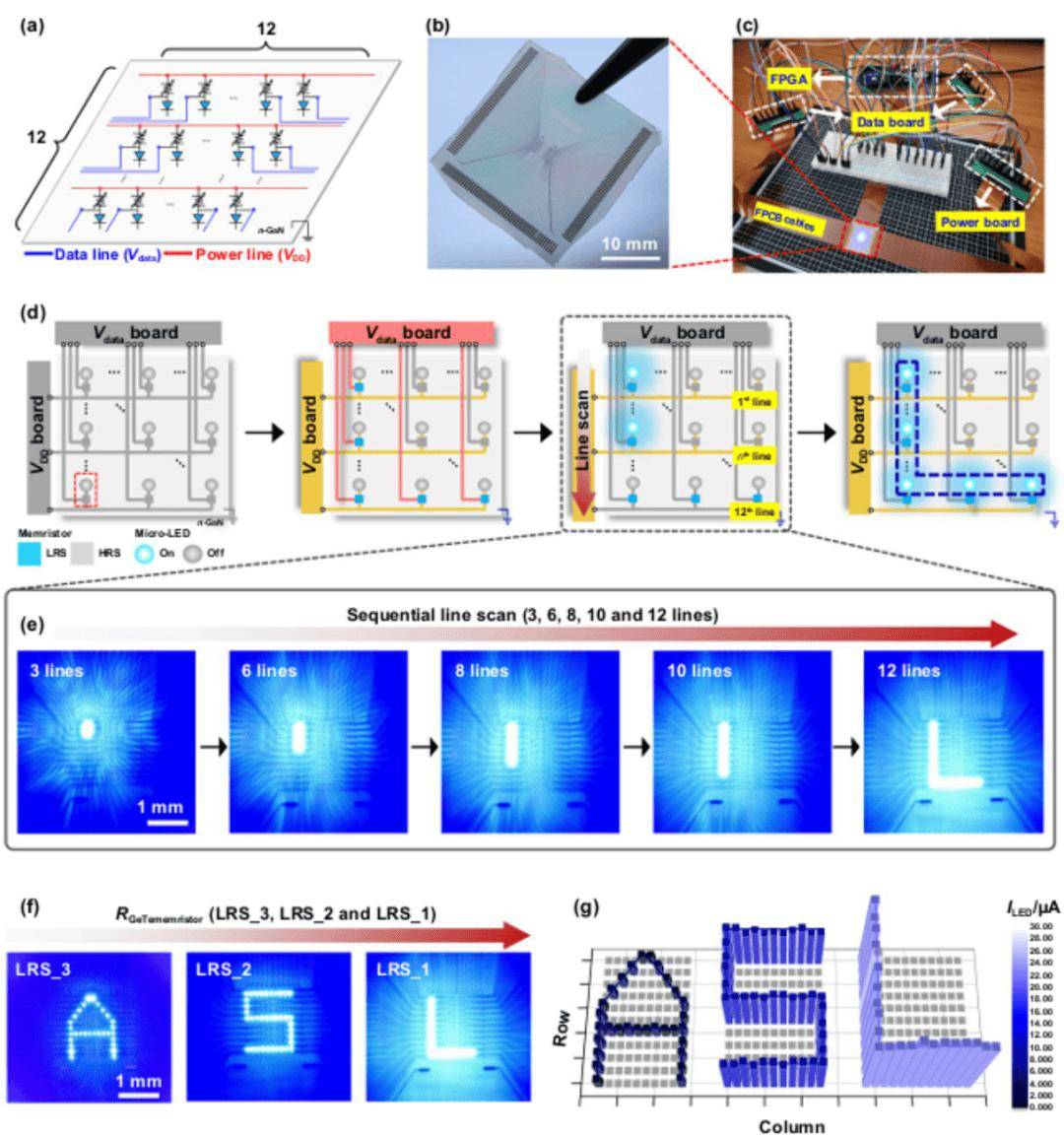

12×12阵列实现清晰字符显示,6000PPI潜力可期

为验证无电容驱动架构的可行性,研究团队设计并制备了基于GeTe 忆阻器的12×12有源矩阵Micro-LED阵列,通过FPGA驱动板实现了像素的独立寻址与亮度调控,并成功完成了字母“A”、“S”、“L”的显示验证,为技术的实际应用奠定了基础。

阵列设计:交叉结构实现精准寻址

该12×12阵列采用 “横向电源线 + 纵向数据线” 的交叉设计,其中电源线(VDD)贯穿每行像素,提供工作电压;数据线(Vdata)则连接每个单元像素中GeTe忆阻器的底部电极,负责施加SET/RESET电压以调控忆阻器的电阻态。这种设计的核心优势在于 “无串扰”—— 通过控制特定行的电源线与特定列的数据线电压差,可精准选中单个像素,避免相邻像素的误触发。例如,当需要点亮某一像素时,仅需对对应数据线施加2.4V电压,电源线施加2.7V 电压,形成0.3V的SET电压差,即可使忆阻器从高阻态切换至低阻态,驱动Micro-LED发光。

显示效果:亮度均匀,字符清晰可辨

实验测试中,研究团队通过调节忆阻器的电阻态,实现了字符亮度的分级显示—— 字母 “A” 采用 LRS_3(低亮度)、“S” 采用 LRS_2(中亮度)、“L” 采用 LRS_1(高亮度),三种亮度的对比度达到2.4:1,肉眼可清晰区分。同时,通过脉冲宽度调制(PWM)技术,团队进一步验证了灰度调节能力:在2.7V固定电压下,将脉冲占空比从20%提升至80%,Micro-LED的发光强度从54nits线性增加至216nits,线性度误差小于5%,满足显示场景对灰度均匀性的要求。

更值得关注的是该架构的“像素密度潜力”。研究人员指出,当前实验中Micro-LED与忆阻器的尺寸分别为30μm与10μm,对应像素密度约651PPI;若通过高精度光刻技术将Micro-LED尺寸缩小至3μm,忆阻器尺寸同步缩小至1μm,像素密度可突破6000PPI,远超当前 AR/VR设备对5000PPI的需求,甚至可满足未来 “视网膜级” 微显示的技术标准。

可联系我们了解报告详情

联系我们

马女士 Ms. Ceres

Email:CeresMa@cinno.com.cn

CINNO 公众号矩阵

扫码请备注:姓名+公司+职位

我是CINNO最强小编, 恭候您多时啦!

CINNO于2012年底创立于上海,是致力于推动国内电子信息与科技产业发展的国内独立第三方专业产业咨询服务平台。公司创办十二年来,始终围绕泛半导体产业链,在多维度为企业、政府、投资者提供权威而专业的咨询服务,包括但不限于产业资讯、市场咨询、尽职调查、项目可研、管理咨询、投融资等方面,覆盖企业成长周期各阶段核心利益诉求点,在显示、半导体、消费电子、智能制造及关键零组件等细分领域,积累了数百家中国大陆、中国台湾、日本、韩国、欧美等高科技核心优质企业客户。